VERILOG HARDWARE DESCRIPTION LANGUAGE

Digital circuit design which has evolved rapidly over last 25 years. earlier digital circuits were designed using vacuum tubes and transistors. Integrated circuits were then invented where logic gates were placed on a single chip. The first IC chips were SSI(small scale integration). By improving the number of components on a single IC, MSI(medium scale integration) has been evolved. and again still improving LSI(large scale integration).With the advent of LSI, designers started getting very complicated and felt the need of automate these processes. Electronic design automation(EDA) technique began to evolve. Still the number increased which given raise to VLSI(very large scale integration). here the number became 1,00,000 transistors on a single chip IC. Eventually, This can not be constructed on a bread board. Computer aided techniques became critical for functionality verification, placement and route at this point.

Designers were now building gate-level digital circuits manually on a graphical terminals. They were used in deriving higher level blocks. As designers got larger and complex, logic simulation assumed an important role in the design process.

importance of hdls

1) Designs can be described at a very abstract level by use of HDLs.

2) Designers can write RTL descriptions without choosing a specific fabrication technology.

3) Logic synthesis tools can automatically convert the design to any fabrication technology.

4) By describing designs in HDLs, functional verification of the design can be done early in the design cycle.

5) Since designers work at the RTL level, they can optimise and modify the RTL description unit it meets the desired functionality.

6) Designing with HDLs is analogous to computer programming.

Design methodologies.

There are two types of methodologies: a top-down and a down-top methodology. In top-down methodology , we define the top level block and identify the sub-blocks that are necessary to build the top level block. We further subdivide the sub-blocks until we come to leaf cells.

whereas, the bottom-top methodology is the counter of the top-bottom methodology.

we now relate these hierarchical modelling concepts to verilog. Verilog provides the concept of module. Module is the basic building block of verilog. Typically, elements are grouped into modules that provide a common functionality which can be used at different design processes. Verilog is both a behavioural and a structural language.

Internals of each module can be defined in four different level of abstraction.Module behaves identically with the external environment irrespective of level of abstraction.

a) Behavioural modelling.

This is the highest level of abstraction by verilog HDL. A module can be implemented in terms of the desired design algorithm without concern of hardware implementation details. Designing at this level is very similar to C programming,

Normally, the higher the level of abstraction, the more flexible and technology-independent the design.

b) Dataflow modelling

At this level, the module is designed by specifying the dataflow. The designers aware of how data flow between hardware registers and how the data is processed in the design

c) Gate level modelling.

The module is implemented in terms of logic gates and interconnections between these gates. Design at this level is similar to the describing a design in terms of a gate level logic diagram.

d) Switch level modelling

This is the lowest level of abstraction provided by verilog. A module can be implemented in terms of switches, storage nodes, and the interconnections between them.

Verilog allows the designer to mix all these abstract level in a design. In the digital design community the term RTL(register transfer level) is frequently used for the verilog description that uses a combination of behavioural an dataflow constructs and is acceptable to logic synthesis tools.

If a design contains four modules, verilog allows each of the module can be written in different level of abstraction. As the design matures, most modules are replaced with gate level implementations.

Instances

A module provides a template from which you create actual objects. when a module is invoked, verilog creates a unique object from the template. Each object has its own name, variable,parameters, and I/O interface. The process of creating objects from a module template is called instantiation. and the object is called instances.In verilog it is illegal to nest modules. One module definition within the module and endmodule.

Simulation

Once the design block is completed, it must be tested. The functionality of the design block can be tested by applying stimulus and checking results. We call such block as STIMULUS block or a TESTBENCH.

This block can be written verilog only hence any other language is not required for that. It is a good practice to write design and testbench program separate.

system tasks and compiler directives

verilog procure you standard system tasks for some routine functions. All these commands are appear in the form of "$<keyword>". Operations such as displaying on the screen , monitoring value of nets, stopping,and finishing are done by system tasks.

Displaying information

1) $display: it is the main system task for displaying values of variables or strings or expressions. This is one of the most useful task in verilog.

usage:- $display(p1,p2,p3.....pn);

p1,p2 can be quoted strings or variables or expressions. the format or a function is very much similar to the the printf function in c

2) $monitor: verilog provides a mechanism to monitor a signal when its value changes. This facility is provided by the $monitor task.

usage:- $monitor(p1,p2,p3.....pn);

the syntax is similar for both task operators but the functionality is different.

3)$stop: is provided to stop during simulation.

usage:- $stop;

The $stop task puts the simulation in an interactive mode. The designer can then debug the design from the interactive mode. The $stop task is used whenever the designer wants to stop and examine the results or states of the registers, nets or ports.

4)$finish: this task used to terminate the simulation

usage:- $finish;

compiler directives

all compiler directives are define by using the "`<keyword>".

1)`define: this directive is used to define the text macros in verilog. The verilog compiler substitutes the text of the macro wherever it counters a `<macro_name>. this is similar to the #define inthe C programming. The defined constants or text macros are used in the verilog code by preceding them with a `(back tick).

2)`include: The `include directive allows you to include entire contents of a verilog source file in another verilog file during compilation. this works similar to include in C.This directive typically include the header files, which typically contain global or commonly used definition.

3)`timescale: Often in a simulation, delay values in one module need to be defined by using a certain time unit e.g. 1microsec, delay values in another module need to be defined by using a different time unit.e.g. 1nanosec. Verilog allows reference time unit for module to be specified with `timescale compiler directive.

usage:- `timescale <reference_time_unit>/<time_precision>.

Verilog is generally worked out or written in a software called XILINX SUITE ISE. which is user-friendly and much similar to C programming.

Now lets see an example program and functionality of every statement.

verilog programming is case-sensitive and every statement should be terminated with ;(semi colon).

the program should end with endmodule.

SAMPLE PROGRAM

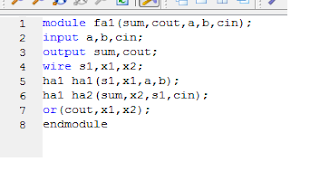

Here, is the program FOR FULL ADDER USING HALF ADDERS

First we need design half adder and with that we can design full adder.

the above program is for the design of half adder which you can see on the right side image.

Lets discuss something about these different statements.

module:- this is the start of the program. We had discussed earlier about module that it is the basic building block of the designing hardware in verilog.

ha1:- This is the name given to the module. where we can differentiate from different modules. Here I have given a ha1 as my module name. Module name should not consist of any blank spaces and it should not start with any number.

(sum,cout, a,b):- these are the list of ports or variables. We need to list the ports by a module name followed by list of ports in the parentheses. here I took sum, cout, a,b as variables. Ports are nothing but a module communicates with external environment using ports.

input, output:-these are called port declarations which says a particular port should behave either input or output port.

now, you can write the program about the functionality of the module using ports and variables.

after completion of it, you can check for any errors by clicking "check syntax" in processes window.

As I explained earlier about instantiation, here in full adder program, I just instantiated the half adder program by a ha1 in line number 5 and 6. By this process the program writing gets simpler.

instantiation is nothing but a process in which variables to the instantiated module are changed.

Now, we completed the writing of source code. this is to be tested. So, we need to write the stimulus block or testbench for this code. The testbench for full adder program as shown below.,

Testbench will also looks like source code but here we give the different inputs to the designed module hence, in the image or program a,b,cin are the given inputs for the full adder circuit. the output of this circuit can be seen by clicking on a "check behavioural simulation".

This is the result or the output of the full adder circuit.

Since, this verilog HDL has many advantages such as easy, flexible, user-friendly. So, this programming is used for many logic designs, state machines, synchronous and asynchronous digital

designs. And it will also very helpful to students in developing the projects on digital system designs.

This is the information gathered from different references books and internet. If you have any feedback or any data was wrong please don't hesitate to write a comment below..